Serial Input Paralel Output Sipo

среда 14 ноября admin 93

Explain how serial in/serial out (SISO), serial in/parallel out (SIPO), parallel. Example of IC: 74HC165, 74HC195 Each clock pulse will move an input bit to.

In, a shift register is a cascade of, sharing the same, in which the output of each flip-flop is connected to the 'data' input of the next flip-flop in the chain, resulting in a circuit that shifts by one position the ' stored in it, 'shifting in' the data present at its input and 'shifting out' the last bit in the array, at each transition of the clock input. More generally, a shift register may be multidimensional, such that its 'data in' and stage outputs are themselves bit arrays: this is implemented simply by running several shift registers of the same bit-length in parallel.

Shift registers can have both and inputs and outputs. These are often configured as 'serial-in, parallel-out' (SIPO) or as 'parallel-in, serial-out' (PISO). There are also types that have both serial and parallel input and types with serial and parallel output. There are also 'bidirectional' shift registers which allow shifting in both directions: L→R or R→L.

The serial input and last output of a shift register can also be connected to create a 'circular shift register'. Contents • • • • • • • • Serial-in serial-out (SISO) [ ] Destructive readout [ ] 0 0 0 0 1 0 0 0 0 1 0 0 1 0 1 0 1 1 0 1 0 1 1 0 0 0 1 1 0 0 0 1 0 0 0 0 These are the simplest kind of shift registers.

The data string is presented at 'Data In', and is shifted right one stage each time 'Data Advance' is brought. At each advance, the bit on the far left (i.e.

'Data In') is shifted into the first 's output. Developer 6i patch 14. The bit on the far right (i.e. Data Out) is shifted out and lost.

The data is stored after each on the 'Q' output, so there are four storage 'slots' available in this arrangement, hence it is a 4-bit Register. Sec542 web app penetration testing and ethical hacking pdf download free softwa. To give an idea of the shifting pattern, imagine that the register holds 0000 (so all storage slots are empty). As 'Data In' presents 1,0,1,1,0,0,0,0 (in that order, with a pulse at 'Data Advance' each time—this is called clocking or strobing) to the register, this is the result. The right hand column corresponds to the right-most flip-flop's output pin, and so on. So the serial output of the entire register is 00001011.

It can be seen that if data were to be continued to input, it would get exactly what was put in (10110000), but offset by four 'Data Advance' cycles. This arrangement is the hardware equivalent of a. Also, at any time, the whole register can be set to zero by bringing the reset (R) pins high. This arrangement performs destructive readout - each datum is lost once it has been shifted out of the right-most bit.

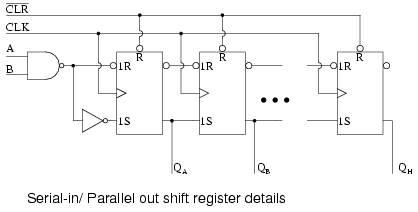

Serial-in parallel-out (SIPO) [ ]. This configuration allows conversion from serial to parallel format. Data input is serial, as described in the SISO section above. Once the data has been clocked in, it may be either read off at each output simultaneously, or it can be shifted out. In this configuration, each flip-flop is. All flip-flops operate at the given clock frequency.